/中文/

/英文/

/中文/

/中文/

/中文/

/多国/

/中文/

/英文/

/英文/

/中文/

7-zip下载v18.03 简体中文美化版

7-zip下载v18.03 简体中文美化版 Bubble Math(泡泡数学)v1.0 电脑版

Bubble Math(泡泡数学)v1.0 电脑版 EditPad Pro(多功能文本编辑器)v7.65 中文版

EditPad Pro(多功能文本编辑器)v7.65 中文版 彗星QQ资源文件读取器v2.1 绿色免费版

彗星QQ资源文件读取器v2.1 绿色免费版 ScanTransfer(无线传输工具)v2018 官方版

ScanTransfer(无线传输工具)v2018 官方版 Easy Equation Solver(在线方程式计算器)v1.8 官方版

Easy Equation Solver(在线方程式计算器)v1.8 官方版 动书编辑器(motionbook)v2018 官方版

动书编辑器(motionbook)v2018 官方版 Flash Renamer(批量重命名软件)v6.9 官方版

Flash Renamer(批量重命名软件)v6.9 官方版 字由客户端v2.0.0.4 官方版

字由客户端v2.0.0.4 官方版 Notepad2书签版(Notepad2 Bookmark Edition)v5.1 官方版

Notepad2书签版(Notepad2 Bookmark Edition)v5.1 官方版软件Tags:

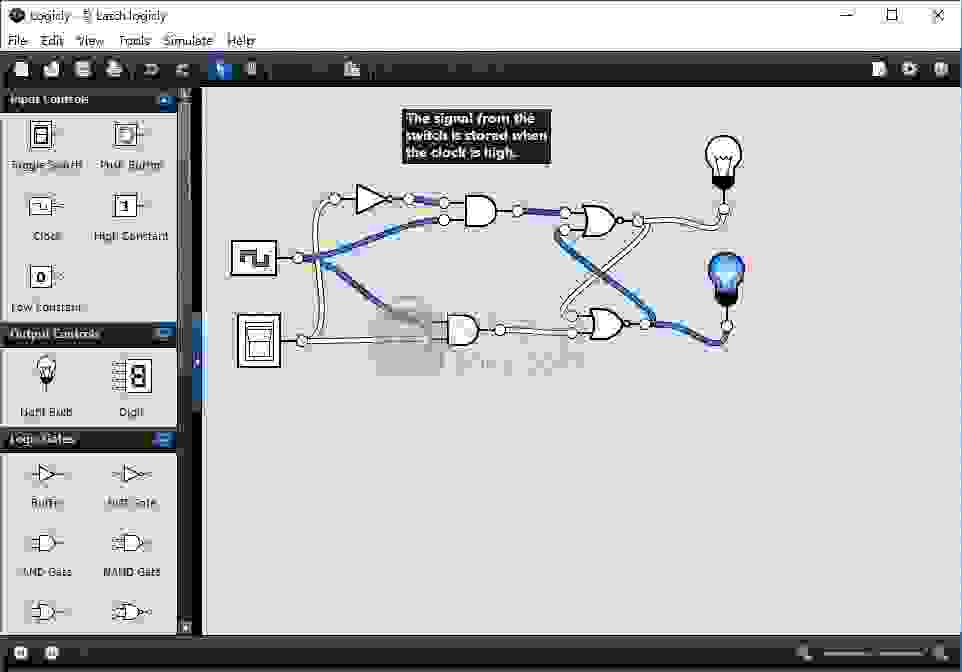

Logicly提供电路设计功能,可以通过这款软件帮助用户配置电路,软件提供很多组件,鼠标点击一个组件就可以拖动到设计区域使用,可以对组件设置名字,可以调整组件属性,添加多个电气组件以后就可以在软件设置连接方式,直接在软件选择电线连接,将各种电路组件连接为一个完整的电路,要创建连接,请单击组件的输出引脚(圆形连接器,通常在右侧),然后将电线拖到未连接的输入引脚上,兼容的引脚将以蓝色突出显示,输入引脚只能连接到单个输出引脚,一个输出引脚可以连接到许多输入引脚,随后在软件测试电路是否可以正常运行,启动模拟运行功能就可以在软件测试电路!

1、运行模拟

创建或打开文档时,Logicly会自动开始模拟。信号将立即在连接的组件之间传播,如果您的电路包含一个或多个Clocks,它们将开始振荡。

2、逻辑和逻辑色彩

信号在Logicly使用颜色表示。当引脚更改状态或创建或删除连接时,连接对象以及某些对象本身的导线可能会在编辑面上更改颜色。

蓝色表示信号处于高状态(true)。

白色表示信号处于低电平状态(假)。

灰色表示信号处于高阻抗状态(hi-Z)。

红色表示信号处于错误状态。

3、定制集成电路

定制集成电路允许您将文档的复杂子集打包为单个可重用组件,类似于触发器。

4、设计电路

从Logicly上讲,您可以将组件拖放到编辑图面上,并使用鼠标轻松地对其进行操作。

使用组件

要将组件添加到文档中,请将其从窗口左侧的组件选择器拖到右侧的编辑表面。释放鼠标左键,将其放在编辑图面上的任何位置。

要选择文档中的单个组件,请用鼠标单击它。它将突出显示为蓝色,表明已被选中。

5、零件和电线

更改对象在编辑面上的外观和行为。

如果愿意,可以在逻辑门符号的不同标准之间更改符号样式。ANSI / IEEE标准提供独特的形状,而IEC标准使用矩形。

可用组件

Logicly提供各种逻辑门,触发器和其他组件,用于设计逻辑电路。

对象类别

人们可以根据其功能将添加到电路中的对象分为几个不同的类别。

输入控件可以将高(真)或低(假)信号传递到电路。有些功能(例如Toggle Switch)可以通过用户输入更改状态。其他时钟(例如Clock)可能会根据时间或模拟控制的其他因素来更改状态。

可以将输出控件连接到输出引脚以显示其当前状态。

逻辑门在其输入引脚的状态上执行布尔逻辑功能。

触发器可以存储一位数据。

其他控件包括不适合其他类别的各种对象。

将来的Logicly版本中可能会添加更多类别。

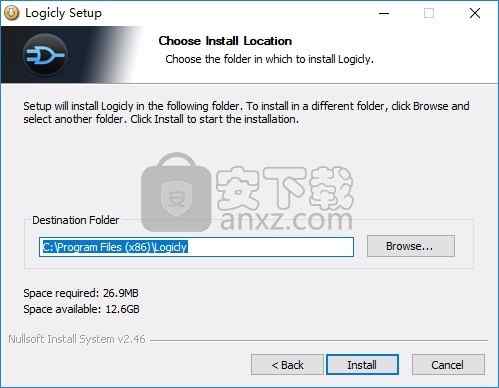

1、打开Logicly-1.7.6.exe软件直接安装,点击next

2、软件的安装地址C:\Program Files (x86)\Logicly

3、提示软件的安装结束界面,点击finish结束安装

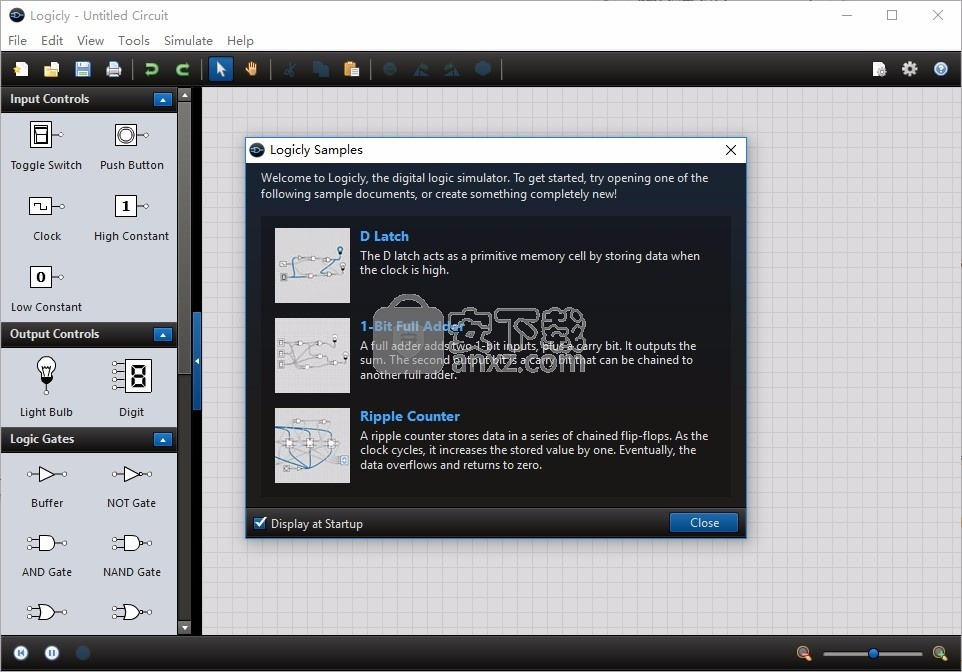

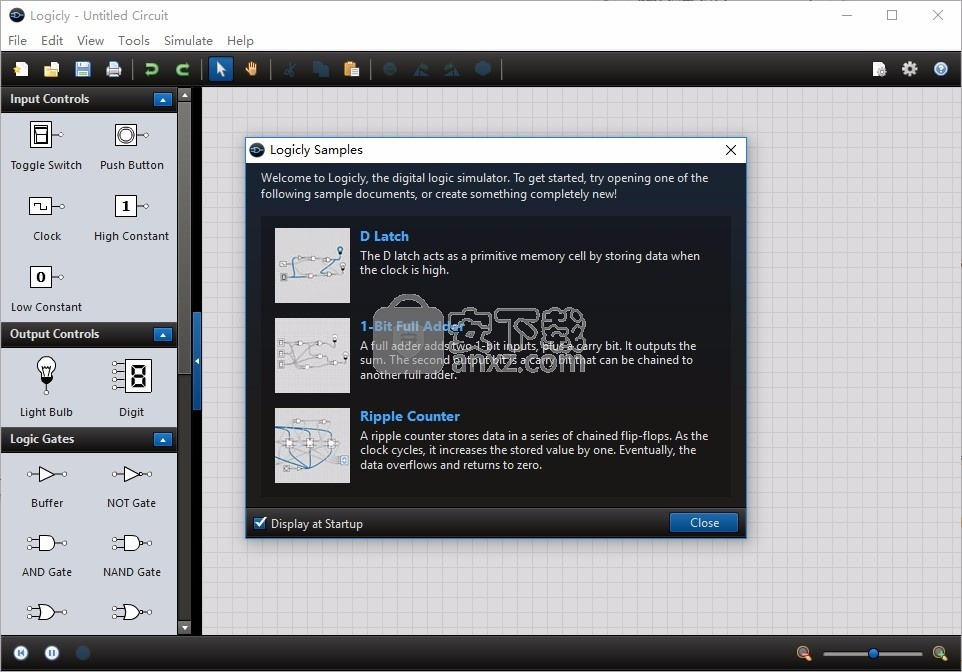

1、打开Logicly提示协议内容,在软件界面接受协议

2、提示试用界面,可以选择试用三十天

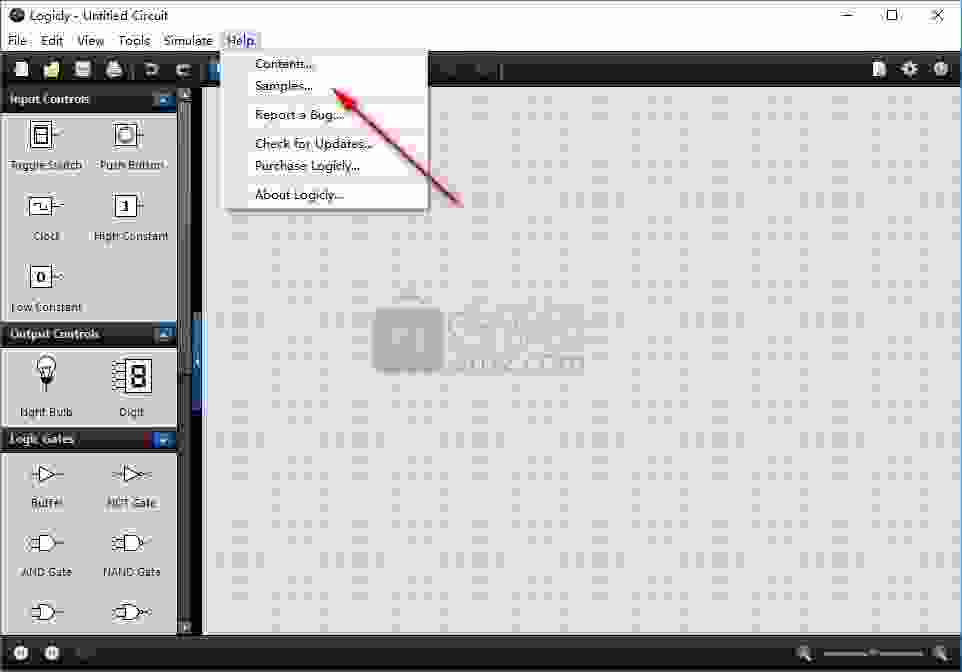

3、欢迎使用Logicly。 首先,请尝试打开以下示例文档之一,或创建全新的文档!

4、D Latch,当时钟为高时,D锁存器通过存储数据充当原始存储单元。

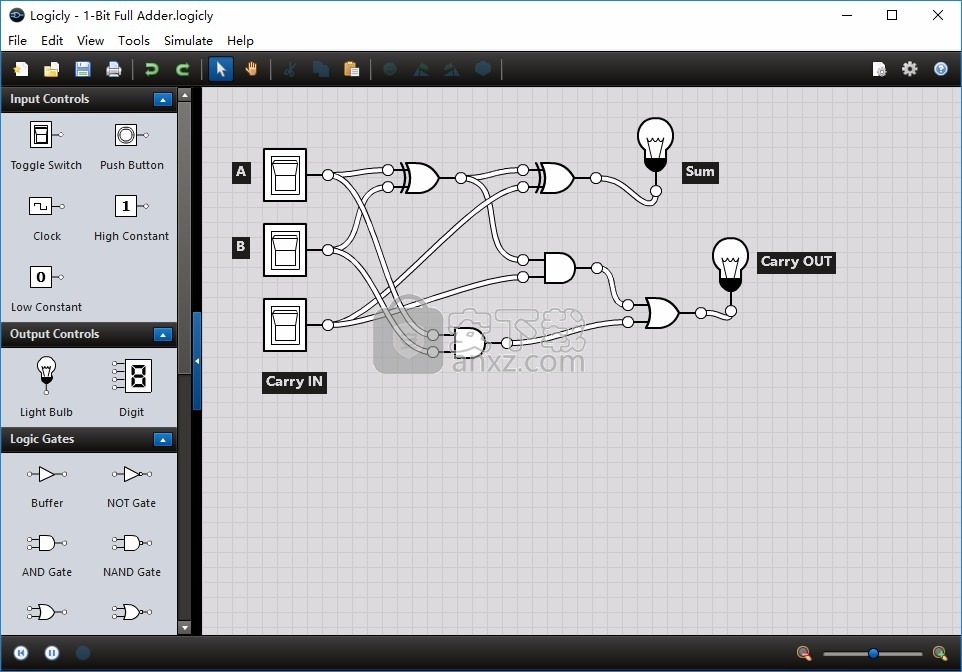

5、1-Bit Full Adder,一个全加法器将两个1位输入加一个进位。 输出总和。 第二个输出位是一个进位位,可以链接到另一个完整的加法器。

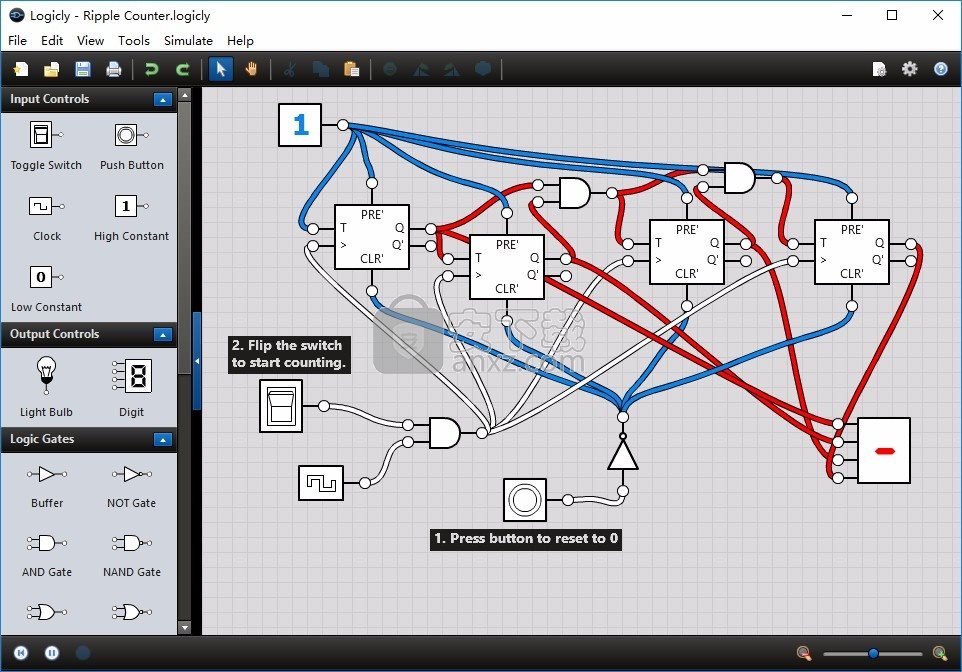

6、Ripple Counter,纹波计数器将数据存储在一系列链接的触发器中。 随着时钟周期,它将存储的值增加一。 最终,数据溢出并返回零。

7、可以在软件查看帮助内容,了解Logicly如何设计电路

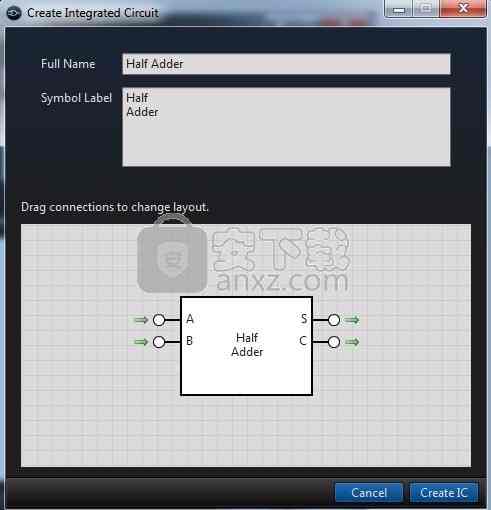

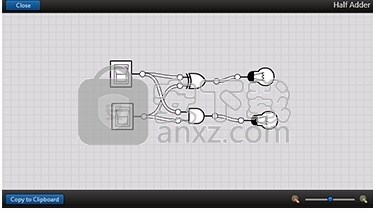

示例:创建自定义半加器

为了更好地演示这是如何工作的,以下部分将引导您为半加法器创建定制集成电路。下面是一个半加法器的现场演示:

首先在Logicly中重新创建上述图。该拨动开关组件将成为输入连接器中的定制的集成电路,而灯泡组件将成为输出连接器。

选择顶部的拨动开关组件。

在属性窗口中,输入A“ 导出名称”输入。导出名称值将显示在您的自定义集成电路上,输入或输出连接器旁边。如果文本很长,则可能会自动将其缩短并附加省略号。

选择底部的拨动开关组件,然后B在属性窗口的“导出名称”输入框中输入。

选择顶部灯泡组件,然后S在属性窗口的“导出名称”输入框中输入(代表“ sum”)。

选择底部的灯泡组件,然后C在属性窗口的“导出名称”输入框中输入(“携带”)。

选择全选从编辑菜单,或拖动周围全半加器电路的选择矩形,如果您的文档包含超过半加器。

从“ 编辑”菜单中,选择“ 创建集成电路...”。

现在,您应该看到“创建集成电路”窗口。当您的选择不包含至少一个拨动开关和至少一个灯泡时,将显示一条错误消息。同样,如果您没有在一个或多个拨动开关或灯泡上设置导出名称,则会显示错误。

在“ 全名”输入框中,输入自定义集成电路的完整详细名称。该文本将出现在“逻辑”主窗口左侧的组件列表上显示的标签中。对于此示例,我们应输入Half Adder。

在“ 符号标签”输入框中,您可以输入一些简短的标签文本以显示在电路符号的中心。该字段是可选的,但为清楚起见建议使用。与上述相同,我们将输入Half Adder。如您在上面的屏幕快照中所见,您可以选择在标签文本中包含换行符。我们还可以考虑使用诸如的缩写,HA以减少编辑器中的空间。

最后,您可以更改每个输入和输出连接器的位置。默认情况下,所有输入都出现在左侧,所有输出都出现在右侧,类似于逻辑门。但是,您可以按任意顺序将任何连接器拖到符号的顶部,右侧,底部或左侧。对于半加法器,我们将所有输入保留在左侧,将输出保留在右侧,但可以根据需要随意将它们拖动到不同的位置。

完成所有操作后,单击“ 创建IC”按钮。

新的定制集成电路将出现在“逻辑”主窗口左侧的组件列表中。您将在列表底部找到一个名为Custom的新类别。要使用新的Half Adder电路,只需将其拖到编辑器中,然后像其他任何组件一样连接到输入和输出。

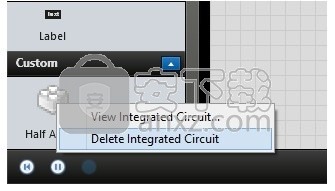

删除自定义集成电路

在Logicly主窗口左侧的组件列表中找到定制集成电路。它应该出现在“ 自定义”类别中。右键单击自定义电路的图标,然后选择删除集成电路。

如果当前文档中正在使用要删除的定制组件,或者在设计中包含了另一个定制组件,则会显示一条错误消息,说明无法删除定制电路。

查看自定义集成电路的内容

创建定制集成电路后,您可以查看其设计,但无法对其进行编辑。在“ 自定义”类别下的“组件”列表中找到自定义集成电路。右键单击并从上下文菜单中选择“ 查看集成电路... ”。父文档将被暂时隐藏,而将显示您的自定义集成电路。在此视图中,您可以平移和缩放以浏览电路,并且所有组件均正常工作。这是一个与主文档完全隔离的独立模拟,因此,如果您选择与组件交互,则不会有任何后果。完成后,单击Logicly主窗口左上角的“ 关闭”按钮以返回到父文档。

或者,要查看定制集成电路的内容,可以在编辑界面上双击其实例。

由于创建后无法编辑自定义集成电路,因此在查看电路内容时可以使用“ 复制到剪贴板”按钮。您可以使用它将内容粘贴回父文档中,以对其进行编辑并创建新的自定义集成电路。

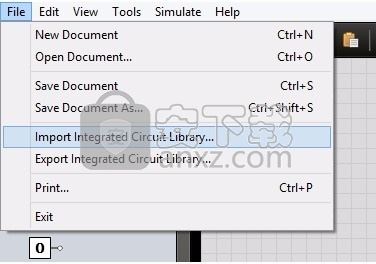

在多个文档之间共享定制集成电路

有两种方法可以将一个文档与另一个文档共享定制集成电路。最简单的方法是在第一个文档的编辑表面上选择任何集成电路,将其复制到剪贴板,然后将其粘贴到第二个文档中。定制集成电路将自动添加到组件列表中,您可以在第二个文档中的任何位置重复使用它,就像您最初在此处创建它一样。

如果您希望在单独的外部文件中管理一组集成电路,则可以将组件列表导出到集成电路库文件。

打开文件菜单,选择导出集成电路库...。将打开一个保存文件对话框,当您选择一个位置时,包含当前文档所有集成电路的逻辑库文件将保存到您的计算机中。

如您在上面的屏幕快照中所见,您还可以从“ 文件”菜单中选择“ 导入集成电路库... ” 。当从计算机中选择一个logiclylib文件时,该文件包含的所有自定义集成电路都将添加到当前文档中。如果当前文档中已存在该库中的任何定制集成电路,则Logicly将不会创建重复的集成电路。您创建的每个新的自定义集成电路都有一个唯一的ID,该ID在添加它的每个文档中都以相同的方式对其进行标识。

使用连接

通过使用“电线”连接组件,信号在电路周围传递。

要创建连接,请单击组件的输出引脚(圆形连接器,通常在右侧),然后将电线拖到未连接的输入引脚上。兼容的引脚将以蓝色突出显示。输入引脚只能连接到单个输出引脚。一个输出引脚可以连接到许多输入引脚。

要删除连接,请单击导线以将其选中,然后单击上方工具栏中的“删除”按钮。或者,您可以右键单击并从上下文菜单中选择“删除连接”。

提示:将鼠标悬停在电线上时,它将重新排列到顶部。如果您的电路特别复杂,这对于确定单根电线的连接位置将很有帮助。

要向连接添加点,请单击导线并拖动。将添加一个点。或者,您可以右键单击导线,然后从上下文菜单中选择“添加点”。

提示:点将与同一条线上的其他点捕捉到相同的垂直和水平位置。使用此功能可以创建完美的直线和90度角。

要从连接中删除点,请右键单击该点,然后选择“删除点”。

对象类型

下列对象可以添加到电路中。

甲拨动开关输出一个高(真)或低(假)信号(从未高阻抗(Hi-Z)或错误)。可以通过单击开关来切换状态。

甲按钮输出低(假)通过默认或信号高(真)信号,当被按下时它。

甲时钟之间振荡高(真)和低(假)信号在一个设定的时间周期,其可以被配置。它的状态由仿真自动更改。

甲高的恒定总是输出一个高(真)信号。

甲低恒定总是输出一个低(假)信号。

甲灯泡显示使用颜色的输出管脚的当前状态。

甲4位数字显示十六进制数(0x0-0xF)从四个输入构成。

甲缓冲器简单地传播它接收到的信号。在现实世界中,如果缓冲器失去强度,它将增强电信号。在Logicly的仿真中,可以使用缓冲区来影响传播时间。

“ 非”门会将高(真)信号变为低(假)信号,或者将低信号变为高信号。

一个与门将执行它的输入信号的布尔AND函数。

阿非门将在其输入端的信号执行一个布尔NAND功能。

一个或门将执行它的输入信号的布尔OR功能。

甲NOR门将执行它的输入信号的布尔NOR功能。

一个XOR门将在其输入端的信号执行一个布尔XOR函数。

的XNOR门将在其输入端的信号执行一个布尔XNOR功能。

如果三态启用的输入为高(true),则三态传播其接收的信号。如果启用输入处于低(假)状态,它将输出高阻抗(hi-Z)信号。

一个SR触发器是触发器中最简单的类型。该主从实现在时钟输入的负沿触发。

甲d触发器存储在时钟的正边缘的数据。它具有用于预置和清除的异步输入,当输入信号为高(true)时这些输入无效。此实现基于IC 7474。

甲JK触发器是在SR触发器的改进,因为它被设计成避免竞态条件时都设置和复位输入为高(真)。像上面的D触发器一样,该JK触发器是正沿触发的,并且它具有用于预置和清除的异步输入,当输入信号为高(true)时它们是无效的。

甲T触发器当T是输入切换其输出高(真)。像上面的D和JK触发器一样,该T触发器是正边沿触发的,它具有用于预置和清除的异步输入,当输入信号为高(true)时它们是无效的。

一个总线可以将多个连接合并成一个单一的连接。它通常与三态缓冲器组合,以通过忽略任何高阻抗(hi-Z)信号而仅从其各种输入输出一个信号。如果总线同时接收到高(真)和低(假)信号,它将输出一个错误信号。

如果上拉的输入为高阻抗(hi-Z),则上拉将输出高(真)信号。所有其他输入信号将被传播而不会发生变化。

如果下拉输入为高阻抗(hi-Z),则下拉输出为低电平(假)。所有其他输入信号将被传播而不会发生变化。

斯沃数控加工仿真软件机械电子 / 429.4M

斯沃数控加工仿真软件机械电子 / 429.4M

NAPCB(彩色抄板软件)机械电子 / 6.6M

NAPCB(彩色抄板软件)机械电子 / 6.6M

立创eda软件机械电子 / 93.2M

立创eda软件机械电子 / 93.2M

斯沃数控加工仿真软件机械电子 / 429.4M

斯沃数控加工仿真软件机械电子 / 429.4M

Altair FluxMotor 2021机械电子 / 286M

Altair FluxMotor 2021机械电子 / 286M

NAPCB(彩色抄板软件)机械电子 / 6.6M

NAPCB(彩色抄板软件)机械电子 / 6.6M

立创eda软件机械电子 / 93.2M

立创eda软件机械电子 / 93.2M

Altair FluxMotor 2021机械电子 / 286M

Altair FluxMotor 2021机械电子 / 286M

altair inspire 2021破解版(结构分析) 附安装教程机械电子 / 2662 MB

altair inspire 2021破解版(结构分析) 附安装教程机械电子 / 2662 MB

Altium Concord Pro 2021(电子元件管理工具) v4.0.1.34 破解版机械电子 / 2150 MB

Altium Concord Pro 2021(电子元件管理工具) v4.0.1.34 破解版机械电子 / 2150 MB

立创eda软件v6.4.20.6 官方版机械电子 / 45.9M

立创eda软件v6.4.20.6 官方版机械电子 / 45.9M

斯沃数控加工仿真软件机械电子 / 429.4M

斯沃数控加工仿真软件机械电子 / 429.4M

win10eplan破解加密狗下载机械电子 / 1.10G

win10eplan破解加密狗下载机械电子 / 1.10G

Antenna Magus破解版2020机械电子 / 1.83G

Antenna Magus破解版2020机械电子 / 1.83G

红外遥控编码分析仪机械电子 / 544KB

红外遥控编码分析仪机械电子 / 544KB

大宝剑串口助手机械电子 / 250KB

大宝剑串口助手机械电子 / 250KB

纸艺大师编辑器(Pepakura Designer)v4.2.4 中文版机械电子 / 17.0M

纸艺大师编辑器(Pepakura Designer)v4.2.4 中文版机械电子 / 17.0M

飞思卡尔烧写工具v13.03 绿色版机械电子 / 1.0M

飞思卡尔烧写工具v13.03 绿色版机械电子 / 1.0M

FlashDLPrint(光固化技术切片软件)v2.1.4 官方版机械电子 / 20.3M

FlashDLPrint(光固化技术切片软件)v2.1.4 官方版机械电子 / 20.3M

solidworks2019中文版(附教程)机械电子 / 10G

solidworks2019中文版(附教程)机械电子 / 10G