/中文/

/中文/

/中文/

/中文/

/中文/

/中文/

/中文/

/中文/

/中文/

/中文/

7-zip下载v18.03 简体中文美化版

7-zip下载v18.03 简体中文美化版 Bubble Math(泡泡数学)v1.0 电脑版

Bubble Math(泡泡数学)v1.0 电脑版 EditPad Pro(多功能文本编辑器)v7.65 中文版

EditPad Pro(多功能文本编辑器)v7.65 中文版 Easy Equation Solver(在线方程式计算器)v1.8 官方版

Easy Equation Solver(在线方程式计算器)v1.8 官方版 ScanTransfer(无线传输工具)v2018 官方版

ScanTransfer(无线传输工具)v2018 官方版 彗星QQ资源文件读取器v2.1 绿色免费版

彗星QQ资源文件读取器v2.1 绿色免费版 Flash Renamer(批量重命名软件)v6.9 官方版

Flash Renamer(批量重命名软件)v6.9 官方版 动书编辑器(motionbook)v2018 官方版

动书编辑器(motionbook)v2018 官方版 字由客户端v2.0.0.4 官方版

字由客户端v2.0.0.4 官方版 Notepad2书签版(Notepad2 Bookmark Edition)v5.1 官方版

Notepad2书签版(Notepad2 Bookmark Edition)v5.1 官方版软件Tags: xilinxise编程工具

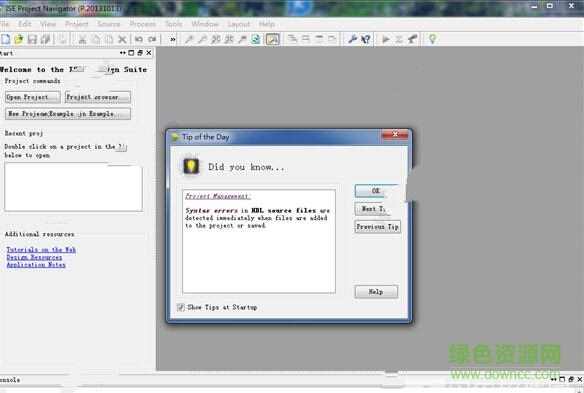

xilinx ise10.1是一款免费的硬件设计工具,可以用来设计仿真挺悠闲,对电路进行模拟测试。集成了多种硬件语言,功能非常给力。需要的用户欢迎在绿色资源网下载安装。

ISE的全称为Integrated Software Environment,即“集成软件环境”,是Xilinx公司的硬件设计工具。相对容易使用的、首屈一指的PLD设计环境 !ISE将先进的技术与灵活性、易使用性的图形界面结合在一起,不管您的经验如何,都让您在最短的时间,以最少的努力,达到最佳的硬件设计。xilinx ise 10.1版本不支持win8等系统,不过在xp系统上完美运行!

1.专门为解决设计人员所面临的时序收敛和生产力这两大艰巨挑战而开发,支持在多台Linux主机上进行分布式处理,可在一天时间里完成更多次实施过程。

2.包括设计输入、仿真、综合、布局布线、生成BIT文件、配置以及在线调试等,功能非常强大。

3.在硬件设计上应用非常广泛,覆盖从系统级设计探索、软件开发和基于HDL硬件设计,直到验证、调试和pcb设计集成的全部设计流程。

4.通过利用分布式处理和多种实施策略,性能可以提升多达38%。SmartXplorer技术同时还提供了一些工具,允许用户利用独立的时序报告监控每个运行实例。

1.综合(Synthesis)

综合是将行为和功能层次表达的电子系统转化为低层次模块的组合。一般来说,综合是针对VHDL来说的,即将VHDL描述的模型、算法、行为和功能描述转换为FPGA/CPLD基本结构相对应的网表文件,即构成对应的映射关系。

2.验证(Verification)

验证(Verification)包含综合后仿真和功能仿真(Simulation)等。功能仿真就是对设计电路的逻辑功能进行模拟测试,看其是否满足设计要求,通常是通过波形图直观地显示输入信号与输出信号之间的关系。 综合后仿真在针对目标器件进行适配之后进行,综合后仿真接近真实器件的特性进行,能精确给出输入与输出之间的信号延时数据。

3.图形或文本输入(Design Entry)

图形或文本输入包括原理图、状态机、波形图、硬件描述语言(HDL),是工程设计的第一步,ISE集成的设计工具主要包括HDL编辑器(HDL Editor)、状态机编辑器(StateCAD)、原理图编辑器(ECS)、IP核生成器(CoreGenerator)和测试激励生成器(HDL Bencher)等。

Redis Assistant(可视化管理监控工具)v1.0.0 免费版编程开发 / 3.9M

Redis Assistant(可视化管理监控工具)v1.0.0 免费版编程开发 / 3.9M

Resource Hackerv5.1.8 绿色版编程开发 / 2.1M

Resource Hackerv5.1.8 绿色版编程开发 / 2.1M

Interbase数据库编程开发 / 248.5M

Interbase数据库编程开发 / 248.5M

Markdown Monster编程开发 / 21.7M

Markdown Monster编程开发 / 21.7M

小码精灵编程电脑客户端编程开发 / 172.1M

小码精灵编程电脑客户端编程开发 / 172.1M

PHP Manager for IIS 7(IIS7配置PHP)编程开发 / 486KB

PHP Manager for IIS 7(IIS7配置PHP)编程开发 / 486KB

信捷XC系列PLC编程软件(XCPPro)编程开发 / 6.6M

信捷XC系列PLC编程软件(XCPPro)编程开发 / 6.6M

核桃编程电脑版编程开发 / 209.3M

核桃编程电脑版编程开发 / 209.3M

Appeon Powerbuilder 2021编程开发 / 1.66G

Appeon Powerbuilder 2021编程开发 / 1.66G

DBeaver数据库连接工具编程开发 / 89.8M

DBeaver数据库连接工具编程开发 / 89.8M

TGraphDisplay3D(图形编程软件)v1.0.59.202 官方版编程开发 / 23.2M

TGraphDisplay3D(图形编程软件)v1.0.59.202 官方版编程开发 / 23.2M

Sencha Architect 3注册版编程开发 / 240.7M

Sencha Architect 3注册版编程开发 / 240.7M

Mongood(MongoDB管理工具)v0.6.2 免费版编程开发 / 9.2M

Mongood(MongoDB管理工具)v0.6.2 免费版编程开发 / 9.2M

Claris FileMaker Pro(低代码开发工具)v19.3.1.43 免费版编程开发 / 289.9M

Claris FileMaker Pro(低代码开发工具)v19.3.1.43 免费版编程开发 / 289.9M

SRPG Studio(RPG游戏制作引擎)v1.149 免费版编程开发 / 191.5M

SRPG Studio(RPG游戏制作引擎)v1.149 免费版编程开发 / 191.5M

sublime text3中文破解版(代码编辑器)编程开发 / 45.6M

sublime text3中文破解版(代码编辑器)编程开发 / 45.6M

navicat data modeler3破解版(数据库设计)编程开发 / 110.4M

navicat data modeler3破解版(数据库设计)编程开发 / 110.4M

CudaText代码编辑器v1.134.1.0 中文版编程开发 / 26.1M

CudaText代码编辑器v1.134.1.0 中文版编程开发 / 26.1M

jsonbuddv6.0.0.0 官方版编程开发 / 20.3M

jsonbuddv6.0.0.0 官方版编程开发 / 20.3M

infragistics2020破解版编程开发 / 2.04G

infragistics2020破解版编程开发 / 2.04G