/中文/

/中文/

/中文/

/英文/

/中文/

/英文/

/英文/

/英文/

/英文/

/中文/

7-zip下载v18.03 简体中文美化版

7-zip下载v18.03 简体中文美化版 Bubble Math(泡泡数学)v1.0 电脑版

Bubble Math(泡泡数学)v1.0 电脑版 EditPad Pro(多功能文本编辑器)v7.65 中文版

EditPad Pro(多功能文本编辑器)v7.65 中文版 Easy Equation Solver(在线方程式计算器)v1.8 官方版

Easy Equation Solver(在线方程式计算器)v1.8 官方版 ScanTransfer(无线传输工具)v2018 官方版

ScanTransfer(无线传输工具)v2018 官方版 彗星QQ资源文件读取器v2.1 绿色免费版

彗星QQ资源文件读取器v2.1 绿色免费版 Flash Renamer(批量重命名软件)v6.9 官方版

Flash Renamer(批量重命名软件)v6.9 官方版 动书编辑器(motionbook)v2018 官方版

动书编辑器(motionbook)v2018 官方版 字由客户端v2.0.0.4 官方版

字由客户端v2.0.0.4 官方版 Notepad2书签版(Notepad2 Bookmark Edition)v5.1 官方版

Notepad2书签版(Notepad2 Bookmark Edition)v5.1 官方版软件Tags:

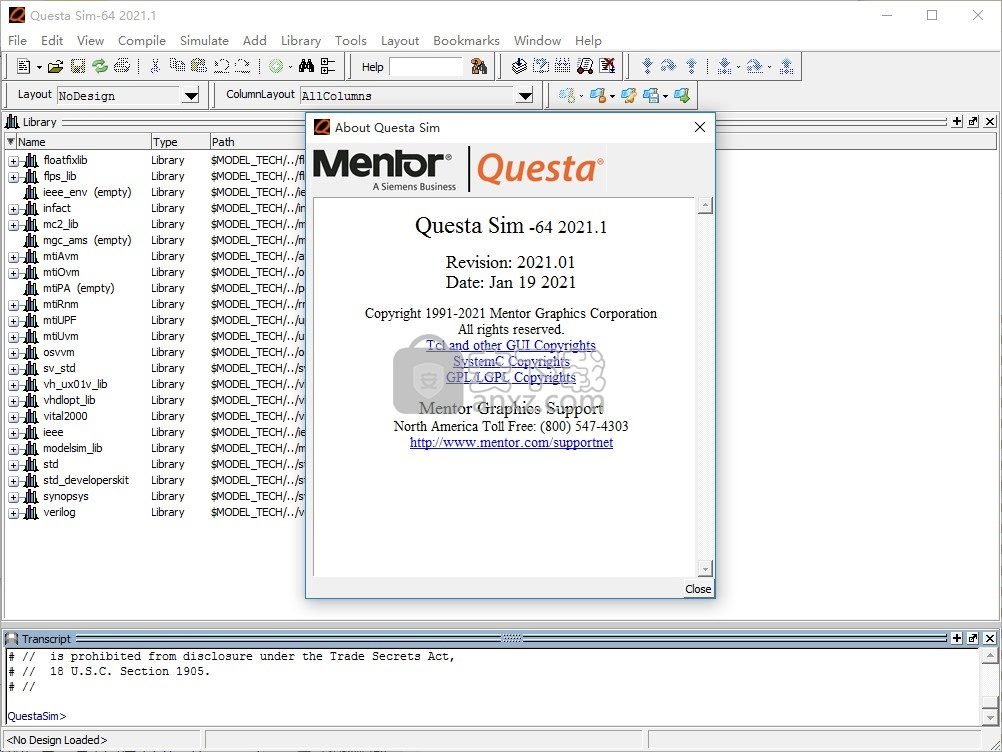

QuestaSim2021破解版是一款仿真软件,可以在软件上配置电气仿真工程,让用户可以在电脑上仿真设计电子设备,软件提供vopt优化设计、VHDL模拟、Verilog和SystemVerilog仿真、SystemC仿真、混合语言模拟等多种方案,可以在软件上快速创建仿真项目,添加项目数据,配置硬件设备,轻松建立新的仿真方案,结合波形图就可以对仿真数据分析,您可以以图形方式生成和编辑波形,然后使用这些波形进行仿真,您可以使用“波形编辑器”四种预定义的模式创建波形,包括时钟,随机,中继器和计数器波形图;QuestaSim2021破解版可以执行的仿真项目还是很多的,如果您需要这款软件就下载吧!

一、使用vopt优化设计

默认情况下,Questa SIM对您的设计执行内置优化,以最大化模拟器性能。

这些优化限制了设计对象的可见性,但是您可以出于调试目的而提高任何对象的可见性,请参阅“保留对象的可见性以进行调试”。

在Questa SIM中用于执行全局优化的命令是vopt。本章讨论vopt功能,优化对设计的影响以及如何自定义vopt在设计中的应用。

二、项目资源

项目是规范或测试下设计的文件和用户定义的设置的集合。至少,一个项目具有一个根目录,一个工作库和“元数据”,它们存储在位于项目根目录下的.mpf文件中。元数据包括:编译器开关设置,编译顺序和文件映射。

项目可能还包括以下项目:

源文件或对源文件的引用

其他文件,例如自述文件或其他项目文档

本地图书馆

引用全球图书馆

模拟配置

资料夹

三、设计库

VHDL设计与库相关联,库是包含已编译设计单元的对象。 Questa SIM中模拟的SystemC,Verilog和SystemVerilog设计也被编译到库中。

四、VHDL模拟

Questa SIM使您能够编译,优化,加载和仿真VHDL设计。

五、波形分析

Wave窗口是在仿真后用于分析和调试设计的最常用工具。 它以波形和信号值的形式显示设计中的所有信号,并提供一套用于调试的图形工具。

六、约束随机刺激的验证

SystemVerilog支持具有随机约束的自动测试平台开发,使您能够自动生成用于功能验证的测试平台。 SystemVerilog提供了一种面向对象的方法,用于指定对随机测试基准值的约束。 然后,Questa SIM使用约束求解器处理这些约束,该求解器生成满足这些约束的随机值。 约束求解器性能分析使您可以查看花费了多少时间来约束哪些约束,以及哪些是最昂贵的约束。 它还可以分析在求解器“区域”中花费的CPU时间,而不是每个函数调用所花费的时间。

七、有限状态机

有限状态机(FSM)反映了从仿真开始到现在的基于状态的设计所经历的变化。 转换指示状态更改,并通过启用它们所需的条件来描述。 由于FSM的复杂性,包含它们的设计可能包含大量缺陷。 因此,在进入设计周期的下一步综合之前,分析RTL中的FSM非常重要。

一、IC设计,验证与制造

1、有效创建世界上最先进的集成电路(IC)

2、创建具有功率,性能,面积和功能的最佳平衡的IC

3、在各个级别进行验证-从C ++原型到芯片测试再到数字孪生

4、满足安全性,功能安全性和芯片生命周期要求

5、借助AI驱动的EDA工具更快地实现覆盖率,签核和更高收益

二、IC封装设计与验证

1、利用完整的高密度高级封装(HDAP)解决方案

2、使用早期的原型设计和计划开发3D封装装配模型

2、更快地执行物理设计,验证,建模和签核

4、今天交付明天的半导体集成创新

三、电子系统设计与制造

1、从单个PCB到系统设计,从个人到企业,均可无缝扩展

2、集成和优化从规格到制造的整个数字流程

3、部署基于模型的高级系统工程方法

4、无论产品的复杂程度如何,均可实现更高的生产率和效率

5、利用数字原型获得更高的性能和可制造性

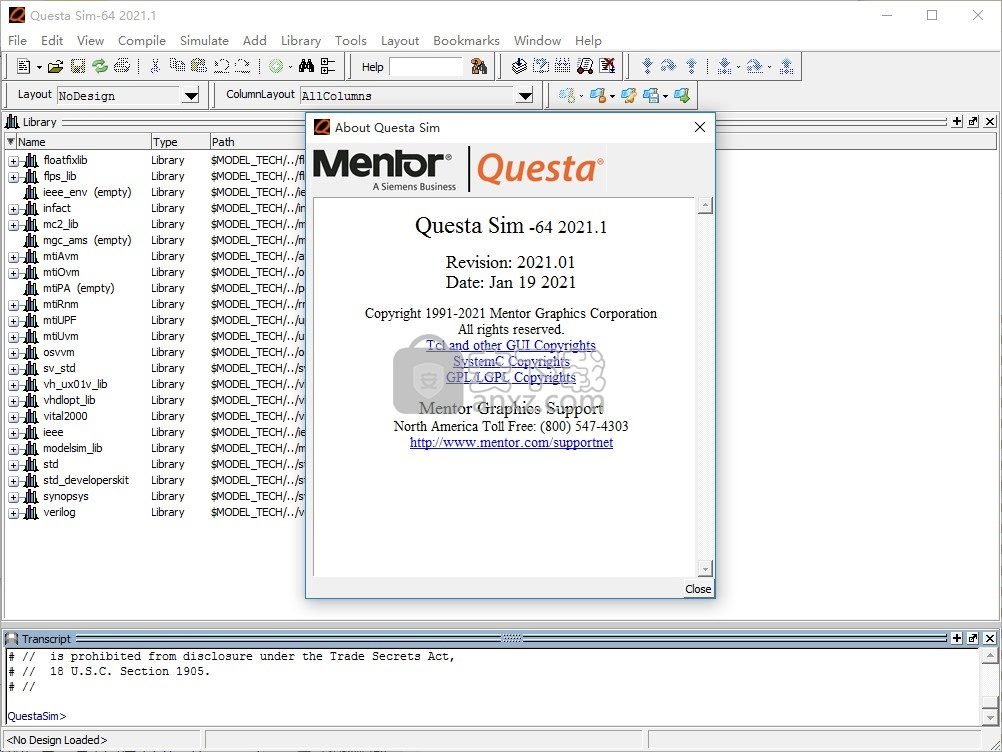

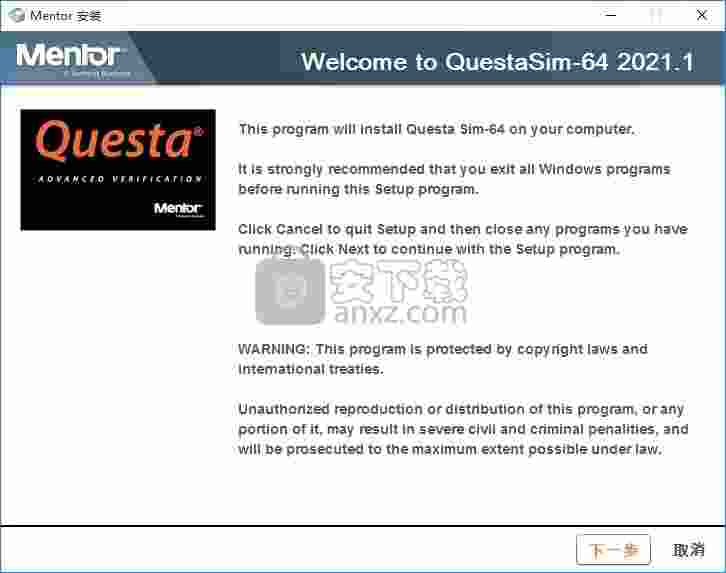

1、打开questasim-win64-2021.1.exe开始安装软件

2、提示软件的安装地址设置C:\questasim64_2021.1

3、小编将软件安装到E盘

4、阅读软件的协议内容,点击同意

5、提示软件的安装过程,等待安装结束

6、提示是否创建桌面启动图标,可以点击是

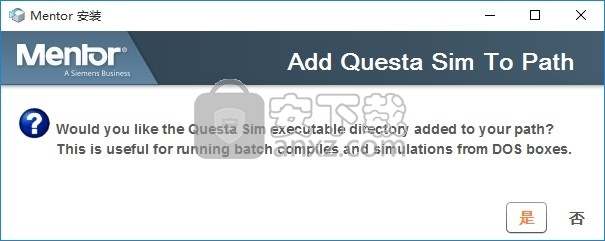

7、提示您想将Questa Sim可执行目录添加到您的路径吗?

这对于从DOS盒运行批处理编译和模拟非常有用,可以点击是

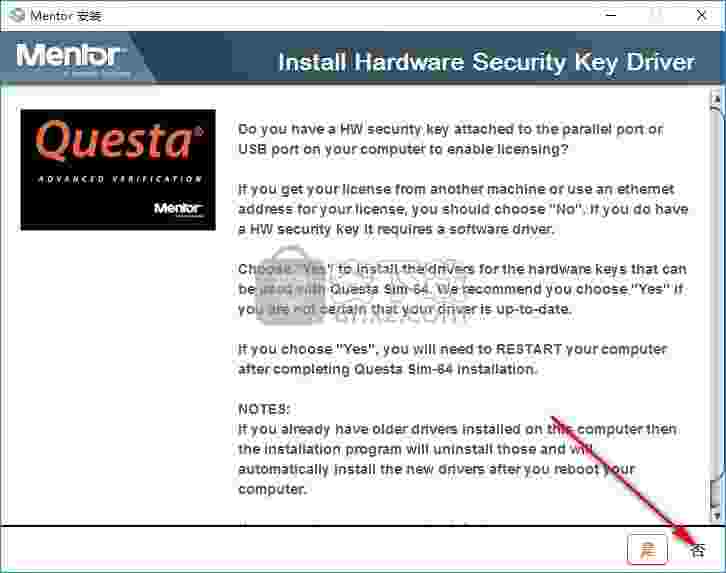

8、提示安装结束,点击否

9、到这里软件就安装完毕了,点击完成

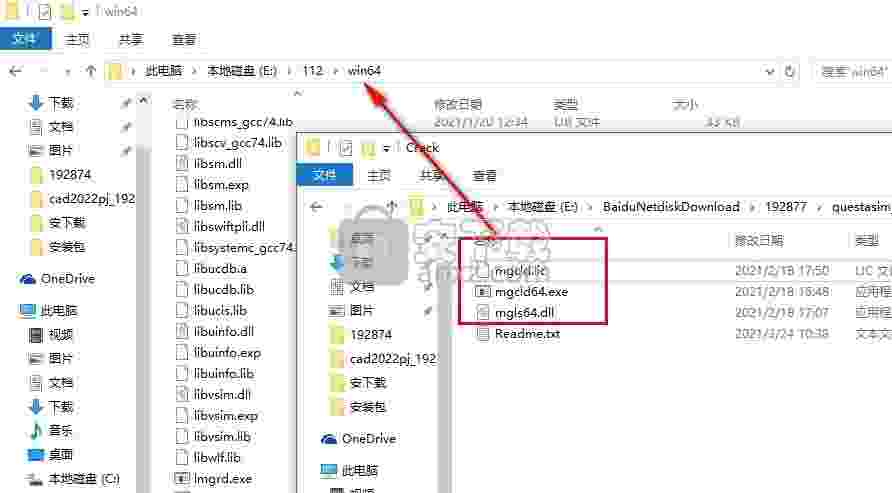

1、将三个补丁复制到软件安装地址下的win64文件夹中替换同名文件

2、选择此电脑-属性-高级设置建立系统环境-创建系统变量

3、变量名称:LM_LICENSE_FILE,变量值E:\112\win64\mgcld.lic(许可证地址),点击确定

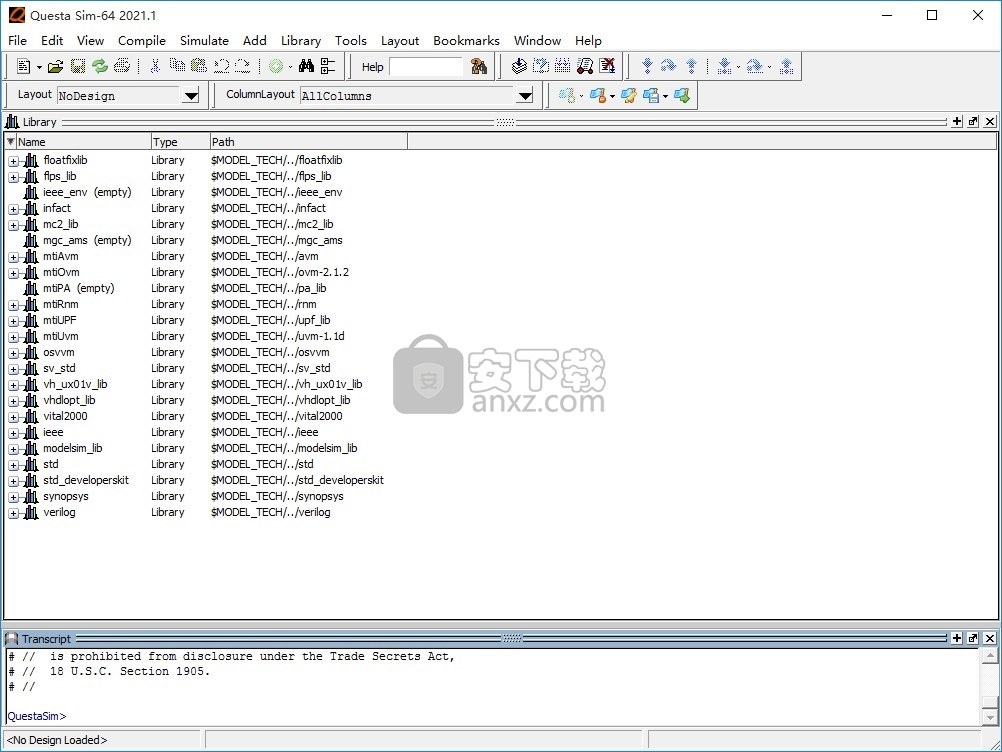

4、打开软件就可以正常使用,这里是软件的启动界面

5、正常进入软件说明激活成功,现在QuestaSim破解完毕

具有功能覆盖范围的验证

功能覆盖范围是用户定义的覆盖范围-与代码覆盖范围形成对比的是,代码覆盖范围是从源头自动推断出来的。在最抽象的层次上,功能覆盖范围指定了在设计或测试平台中某些时间要观察的一些值,并对这些值出现的次数进行计数。

但是,应该注意的是,完整的功能覆盖范围(100%覆盖范围)不一定表示设计正确性,甚至不一定已观察到所有错误。相反,功能覆盖率是置信度指标。它是测试平台的一种实现,这是模拟器跟踪运行测试平台时按预期发生的某些值和事件的一种方式。如果测试平台是全面的,并且覆盖率模型(功能覆盖率指标集)正确地实现了测试台,并且设计能够以100%的功能覆盖率产生正确的结果,那么就可以高度肯定地发现了所有重要的错误。 。

SystemVerilog通过Covergroups和Cover指令实现功能覆盖(有关Cover指令的更多信息,请参见“带有断言和Cover指令的验证”)。由于Cover指令通常是临时的,并且可以在同一评估中检查多个信号和状态,因此设计人员通常将它们作为“白盒”测试插入设计源中-也就是说,它们指定并验证设计的预期行为。这使验证工具可以在发生特定事件或违反假设时进行观察(并记录)。

由于Covergroups是根据整数值操作的,并且具有有限的时间特征,因此它们通常作为“黑匣子”测试插入到测试台本身中。即,由Covergroup监视的值通常是高级测试平台或设计功能,例如事务类型,模式,地址,操作码等。

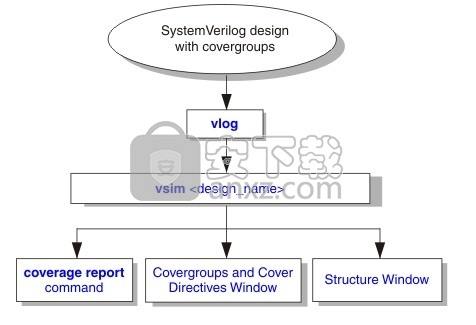

功能覆盖流程

Questa SIM中的SystemVerilog功能覆盖流程分为三个主要步骤:设计文件的编译,仿真和数据分析。

图1. SystemVerilog功能覆盖流程

当源文件以.sv结尾或您为vlog命令指定-sv参数时,Questa SIM会与其他SystemVerilog代码一起编译SystemVerilog功能覆盖结构。

在设计的顶层调用vsim时,模拟器会自动处理存在的所有功能覆盖结构。 运行模拟后,您可以选择在GUI中使用诸如覆盖率报告之类的命令以交互方式查看覆盖率。 您也可以使用coverage save命令将coverage数据保存到(UCDB),这有助于报告,合并和排序coverage数据以及其他类型的验证分析。

功能覆盖率控制选项

SystemVerilog提供了一组用于配置掩护组,掩护点以及穿越option和type_option结构的工具。使用适用于每个设置的准则,这些结构可用于控制SystemVerilog仿真的各个方面。

功能覆盖控制准则

通过命令行界面或.do文件中的change命令控制Questa SIM中的功能覆盖行为,以调整option和type_option结构中包含的变量的值。

例如:

更改covervar.type_option.weight 20

如果在covergroup语法级别上设置,此命令将指定此covergroup的权重,以计算已保存数据库的总体累积(或类型)coverage。如果在覆盖点(或交叉)句法级别设置,它将指定覆盖点(或交叉)的权重,以计算封闭的覆盖组的累积(或类型)覆盖范围。

请注意,在命令行界面中,不能使用类型名称和“ ::”来访问type_option。而是通过实例化的covergroup变量引用type_option,如上面的示例所示。

控制功能覆盖率集合

Questa SIM支持多种启用/禁用功能覆盖范围收集的方法。在实时模拟过程中,可以使用以下任何一种方法从源代码中关闭covergroup,coverpoint和cross的coverage统计信息收集:

使用类型为“位”的SystemVerilog扩展option.no_collect,option.no_collect的默认值为0,这将启用coverage的收集。将该值设置为1将禁用coverage收集(请参见图1)。

如果在源代码中将option.weight设置为0(另请参见SVCovergroupZWNoCollect modelsim.ini变量),则在启用vsim -cvgzwnocollect的情况下进行模拟可以禁用所有零加权项的coverage集合。

使用vsim -nocvg进行仿真会禁用covergroup对象的构建,并会失去在仿真过程中运行内置Covergroup方法的功能。在仿真中使用-nocvg时,不需要虚拟化许可证。

要打印已主动选择进行非收集的功能覆盖项的报告,请对覆盖率报告或vcover report命令使用-nocollect。

图1.使用option.no_collect关闭Coverpoint的收集

控制聚集箱的存在和可见性

默认情况下,将显示covergroup实例(及其中的垃圾箱),而与它们的option.per_instance值无关。但是,仅当type_option.merge_instances = 1时,类型coverage下的聚合箱才可用。在指定如何在给定的covergroup类型中设置merge_instances时,可以从三种可能性中进行选择:

在SystemVerilog代码中设置为0 -此算法选择不存在聚合箱。

在SystemVerilog代码中设置为1 -确实存在聚合箱。

未设置-在这种情况下,Questa SIM默认值是根据“ SystemVerilog 2009 type_option.merge_instances”部分中概述的指示确定的。如果工具选择将其设置为0,则您将没有任何汇总的bin,或者可以在运行时使用vsim -cvgmergeinstances覆盖默认工具设置。

使用modelsim.ini变量SVCovergroupMergeInstancesDefault可以实现相同的行为。

使用UCDB文件控制优化

您可以将功能覆盖数据库(UCDB文件)加载到仿真中,并通过将vsc命令与-cvgprecollect参数一起使用,以控制优化覆盖。

当在输入UCDB中预先覆盖Coverpoint,Cross或Covergroup实例时(即覆盖率是100%),-cvgprecollect参数的存在会指示模拟器在新的模拟中禁用匹配的实例。为实例启用优化后,该实例将从仿真中删除,因此不会收集覆盖数据或将其保存到UCDB中。

优化并非总是可能的。例如,如果某个掩护点参与了交叉,则不能禁用它,因为对交叉进行采样可能需要对掩护点进行采样。在这种情况下,将按照正常模拟的方式处理coverpoint,cross或covergroup实例。

预定义的覆盖方法

SystemVerilog LRM定义了两个内置方法get_coverage()和get_inst_coverage(),它们应用于Covergroup,coverpoint和跨范围。这两个内置插件均以一个浮点数返回coverage指标,该浮点数以百分比形式表示已实现的coverage(其中100.0是最大可能的coverage)。有关这些方法的详细信息,请参阅IEEE Std 1800-2017 LRM,第19.8节。

预定义的覆盖系统功能

SystemVerilog LRM将内置的$ get_coverage()系统功能定义为所有coverage组类型的整体coverage。覆盖组范围内的变量type_option.weight用于加权单个覆盖组对总体累积(或类型)覆盖范围的贡献。

请记住,如上一节所述,不同的模块实例会创建不同的Covergroup类型,$ get_coverage()系统任务将返回加权平均值,如下所示:

分子-所有Covergroup类型的总和(type :: get_coverage()value * type :: type_option.weight)

分母—所有(type :: type_option.weight)的covergroup类型的总和

SystemVerilog功能覆盖术语

LRM指的是累积覆盖率和类型覆盖率。本文档使用术语“基于类型的覆盖率”。 LRM有时会交替使用coverage和instance coverage。本文档使用基于实例的覆盖范围。

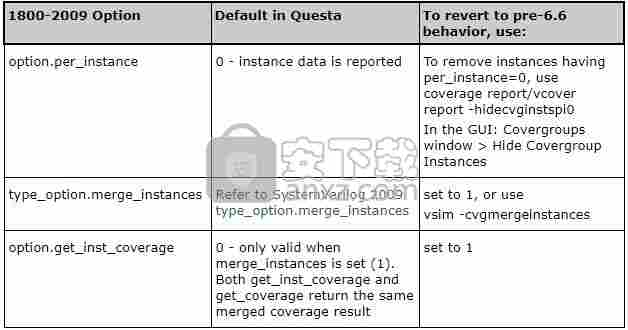

EEE Std 1800-2009选项行为

SystemVerilog覆盖组(Questa SIM版本6.6及更高版本)的覆盖系统默认行为符合对最新IEEE Std 1800-2009及更高版本所做的更改。

笔记:

本节中讨论的命令行选项对coverpoint或cross选项没有影响,因此此处不讨论这些选项。有关完整的详细信息,请参见LRM。

表1汇总了与Covergroup计算和报告有关的更改以及还原设置的说明。

表1. Questa SIM和SystemVerilog IEEE 1800-2009选项

GUI中的功能覆盖范围统计

SystemVerilog覆盖率统计信息显示在Covergroups和Structure(sim)窗口中。

笔记:

封面组是在模拟过程中动态创建的。 这意味着除非您运行模拟,否则它们将不会显示在GUI中。

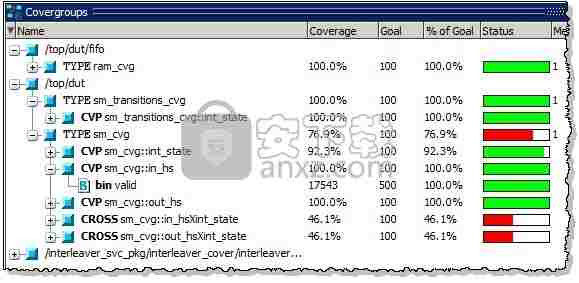

在Covergroups窗口中查看功能Coverage统计信息

您可以在Covergroups窗口中查看功能coverage统计信息,以评估评估验证过程的状态。

程序

1、从主窗口菜单栏中选择查看>覆盖率>覆盖组。

2、运行模拟。 (在运行模拟之前,覆盖组不会显示在“覆盖组”窗口中。)

图1. Covergroups窗口中的功能覆盖率统计

3、Covergroups窗口显示每个Covergroup,coverpoint,cross和bin的Coverage。 Covergroup覆盖率是组成覆盖点和交叉的覆盖率的加权平均值。

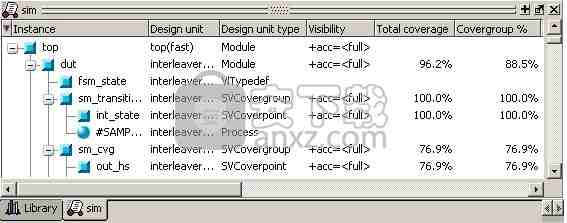

结构窗口中的功能覆盖聚合

访问:查看>结构

某些数据列出现在此窗口中,这些列与“结构”窗口中的功能覆盖率统计信息特别相关。

对象

列标题。

Covergroups%—此列显示子树中所有基于Covergroup类型的Coverage和Cover Directive Coverage的加权平均值。覆盖组覆盖率是使用get_coverage()方法和type_option.weight权重计算的。

Cover指令%-此列显示使用您设置的权重的加权平均值(请参阅“ Weighting Cover指令”)。默认情况下,cover伪指令与Covergroup类型的权重相等。

断言%-此列显示使用断言总数和覆盖的断言数的计算。覆盖断言的数量是所有从未失败的断言,并且通过计数(如果可用)大于0。如果不存在通过数,则覆盖断言的数量与具有以下条件的断言的数量相同:从未失败。

结构窗口中的覆盖范围汇总

汇总的覆盖率数据显示在“结构(sim)”窗口的“总覆盖率”列中。

覆盖范围统计信息是针对本地实例或递归计算的。数据在每个设计区域的基础上包括以下内容,其中设计层次结构的每个子树都有自己的一组指标:

封面组

掩盖指令

断言覆盖

代码覆盖率

图1.结构窗口中的汇总覆盖率数据

“结构”窗口包括“总覆盖率”列,默认情况下,该列以递归方式显示子树中所有覆盖率类型的加权平均值,包括:

基于覆盖组类型的覆盖率

覆盖指令覆盖

代码覆盖率

断言覆盖

方法和type_option.weight权重

保护盖指令使用您设置的权重进行加权(请参阅“保护盖指令加权”)。默认情况下,cover伪指令与Covergroup类型的权重相等。

当禁用“结构”>“代码覆盖率”>“启用递归覆盖率求和”的默认选择时,仅当前设计实例本地的构造才占总覆盖率数。在这种模式下,“总覆盖率”列将单独显示每个设计实例的覆盖率信息,并且不会考虑子实例的贡献。

功能覆盖率报告

您可以使用可通过GUI访问的对话框或在命令行提示符下输入命令来创建功能覆盖率报告。

通过GUI创建文本报告

您可以使用以下任何一种方法来保存功能范围文本报告。

在Cover Directives窗口处于活动状态的情况下,从主菜单中选择Cover Directives>报告。

右键单击“ Cover Directives”窗口中的任意位置,然后从弹出菜单中选择“报告”。

在Covergroups窗口处于活动状态的情况下,从主菜单中选择Covergroups> Report。

右键单击Covergroups窗口中的任意位置,然后从弹出菜单中选择“报告”。

这些操作中的任何一个都将打开“功能覆盖率报告”对话框。

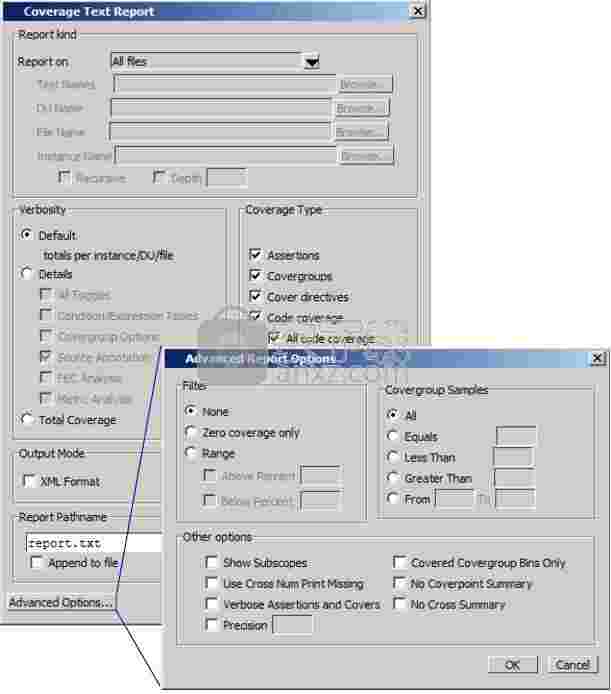

您可以通过选择工具>覆盖率报告>文本来创建具有功能覆盖率统计信息的ASCII文件。这将打开Coverage Text Report对话框(图1)。

图1.创建功能覆盖率文本报告

使用Coverage Text Report对话框可创建有关特定实例或所有Coverage项目的功能Coverage报告。使用选项,您可以仅报告涵盖组或指令覆盖率。如果选择了Covergroup Coverage,则将使用Covergroup类型的对象创建功能覆盖率报告。

关于覆盖率报告,需要牢记以下几点:

筛选不会影响汇总统计信息的计算。它仅影响报告中显示的数据。

报告响应为“不匹配”表示该报告为空。

将对报告进行排序,以使所有计数为0的垃圾箱都显示为第一行。然后,在0计数行的第一部分中,covergroups将是辅助数据类型。因此,封面组A中的所有零值将彼此相邻出现,对于封面组B和其他情况,依此类推。

生成HTML覆盖率报告

您可以使用HTML创建屏幕覆盖率报告,其中包括功能覆盖率合并视图。

为了获得最佳结果,应使用支持以下内容的浏览器查看报告:

JavaScript —如果没有这种支持,您的浏览器将可以运行,但是该报告在美观方面并不令人满意。

Cookies-为了方便查看HTML页面中的覆盖范围项目,您应该启用cookie。

框架和级联样式表(CSS)-尽管建议支持框架,但是如果没有此支持,报告仍可以显示在浏览器中。 报表编写器使用CSS来控制演示文稿,并且最好使用支持框架和CSS的浏览器进行查看。

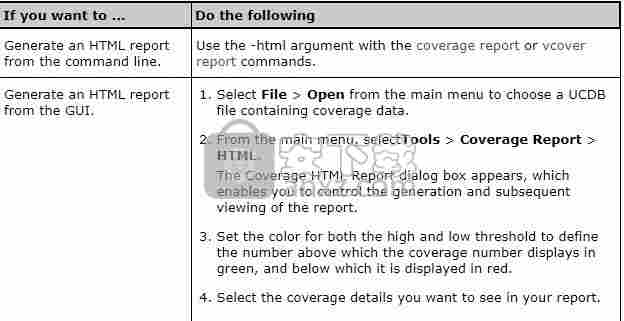

程序

使用以下方法之一生成一份覆盖率报告:

图1. Coverage HTML Report对话框

结果

HTML报告(index.html)被写入指定的目录(默认为/ covhtmlreport)。

您可以在网络浏览器中查看HTML文件。 有关示例,请参见图2。

图2. HTML覆盖率报告摘要

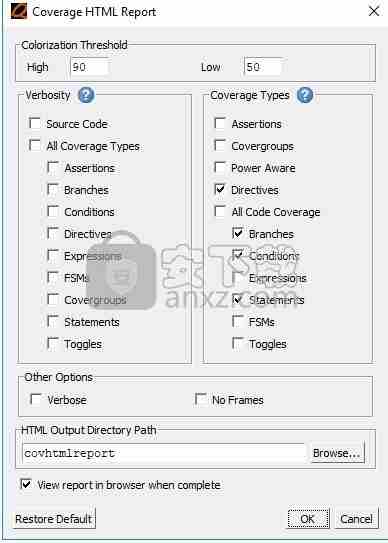

Questa覆盖率报告摘要页面分为多个主要区域。

导航按钮-报告的右上角包含按钮,无论您在报告中的何处导航,这些按钮均保持可用:

主页—导航至HTML覆盖率报告摘要页面。

设计单位-导航到按设计单位组织的coverage摘要。

该表包含所有险种的险种百分比,并且可以按总险种或任何险种类型进行排序。

测试-仅当您使用‑testdetails参数生成报告时才显示,此按钮可将您导航到报告中包含的已记录测试的摘要。

测试计划—仅在使用测试计划时才显示,此按钮会将您导航到一个页面,该页面跟踪您的测试计划部分的覆盖范围。

“测试计划摘要”页面中的覆盖率编号是根据《验证管理用户手册》中“测试计划中的覆盖率计算”中显示的算法计算的。

中心窗格包含显示多种类型的高级覆盖摘要的部分:

测试摘要-仅当您使用‑testdetails参数生成报告时,测试摘要才会显示,测试摘要将显示一个饼状图,代表报告中测试的整体状态。

实例覆盖率摘要-包含使用表1中所述的算法和权重计算得出的覆盖率数字。

实例覆盖率摘要(图3)包括指向功能覆盖率合并视图的Covergroups,Directives和Assertions超链接。

设计单位覆盖范围摘要-显示总体设计单位覆盖范围摘要。此信息也包含在“设计单位覆盖率”页面中对设计单位覆盖率的更详细介绍中。

左侧导航窗格-使您可以按实例或设计单位导航和搜索coverage数据。

Web浏览器使您可以浏览设计的层次结构,就像浏览文件系统一样。生成设计源代码的彩色副本,并将其链接到报告中的适当位置。

图3.实例覆盖率摘要

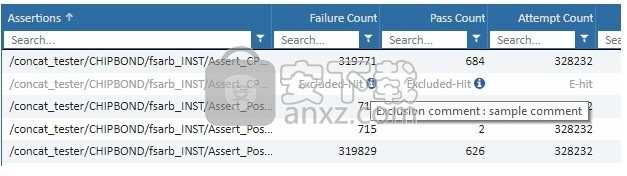

当您将鼠标悬停在用蓝色信息图标表示的点击计数单元格上时,使用coverage exclude -comment命令添加的排除注释将显示为工具提示。信息图标将添加到该单元格,以指示它包含排除注释。例如,当您将鼠标悬停在显示Assert_CPU_Write断言失败计数的单元格上时,图4显示排除注释“排除注释:示例注释”。

图4.排除注释显示为工具提示

与其他类型的覆盖率报告相比,HTML报告的生成会导致计算机对磁盘空间,内存使用率和运行速度问题特别敏感。通过Coverage HTML Report对话框中的单选按钮和coverage report -html选项,许多HTML报告选项都旨在提高报告生成的速度和性能。此外,您可能希望通过排除特定的险种和/或缩小报告中项目的范围来确定报告的目标。

筛选功能覆盖率数据

您可以过滤GUI中显示的功能coverage数据-包括“断言”,“ Cover指令”和“ Covergroups”窗口。

程序

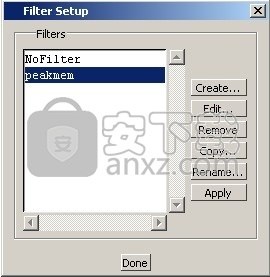

激活所需的窗口,并使用上下文相关菜单下拉菜单,然后选择“过滤器设置”(“覆盖组”>“过滤器”>“设置”,或“覆盖指令”>“过滤器”>“设置”或“断言”>“过滤器”>“设置”)。这将打开“过滤器设置”对话框(图1)。

图1.过滤器设置对话框

要创建一个新的过滤器,请单击“创建”按钮以打开“创建过滤器”对话框(图2)。

图2.创建过滤器对话框

单击“过滤器设置”对话框中的“编辑”按钮可打开“编辑过滤器”对话框,该对话框包含与“创建过滤器”对话框相同的所有功能。

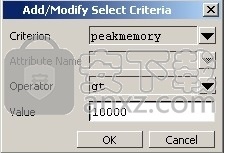

单击添加按钮,将条件,属性,运算符和值添加到“添加/修改选择条件”对话框中的过滤器中(图3)。

图3.添加-修改选择条件对话框

“条件”字段包含一个与“断言”,“覆盖指令”和“覆盖组”窗口中的列相对应的下拉列表,使您可以根据一个或多个特定列中的值来过滤显示。

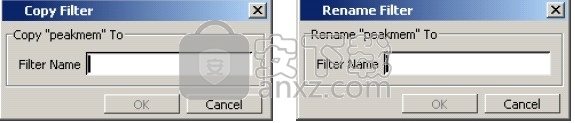

您可以通过单击“过滤器设置”对话框中的“复制”按钮,将条件从现有过滤器复制到另一个过滤器中,这将打开“复制过滤器”对话框。或者,您可以通过单击“重命名”按钮并打开“重命名过滤器”对话框来重命名过滤器。

图4.复制和重命名过滤器对话框

您刚刚创建的过滤器出现在“过滤器设置”对话框的“过滤器”列表中(图1)。

选择“应用”立即过滤显示的数据,或者选择“完成”退出对话框。

通过命令行报告

有两个命令可生成功能覆盖范围统计信息的文本报告。

覆盖率报告

vcover报告

使用vcover report命令,可以在未加载模拟时从保存的功能覆盖率统计信息生成平面或分层的文本报告。

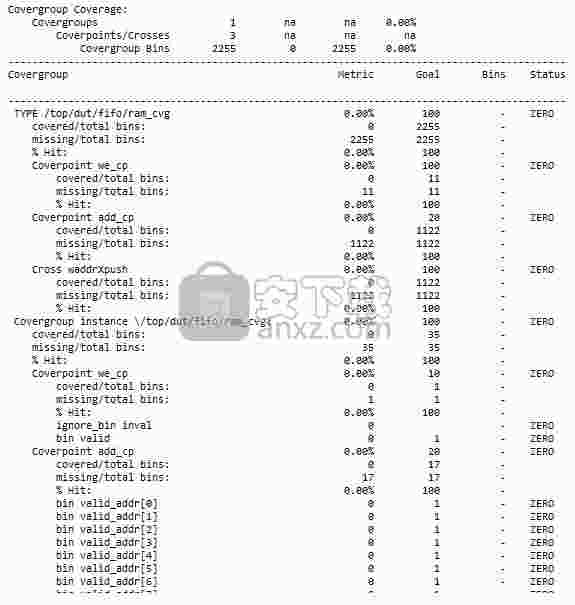

以下是使用vcover report命令从保存的数据中输出的示例报告。

图1. vcover report命令的示例输出

您可以将-hierarchical参数与vcover report命令一起使用,以产生类似于GUI中显示的层次文本输出。您可以将-hierarchical自变量与-instance(例如实例层次结构)一起使用,或-du(用于设计单位层次结构)。以下示例说明了两种报告类型。

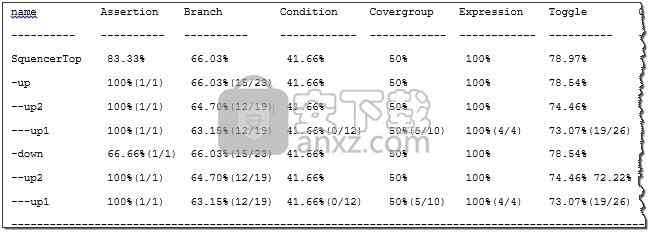

图2显示了按实例组织的分层文本报告的示例输出。

vcover报告-instance = / *。 -分层

图2.分层实例文本报告

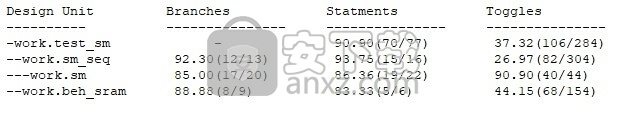

图3显示了由设计单位组织的分层文本报告的示例输出。

vcover报告-du = *-分层

图3.层次设计单元文本报告

默认情况下,这些报告包含covergroup和cover指令的coverage统计信息。您可以为coverage report或vcover report命令指定-covergroup或-directive选项,以分别仅报告coverage组coverage或仅报告coverage指令coverage。

收集FSM覆盖率指标

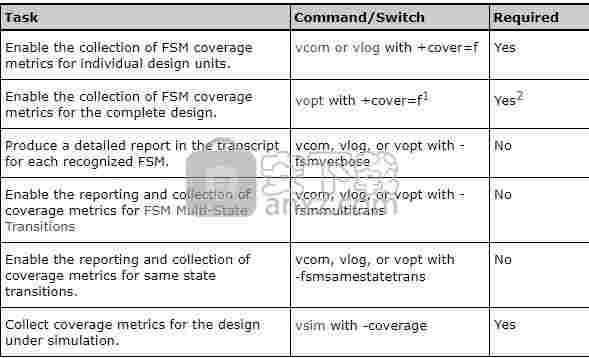

您可以通过在仿真流程中使用命令参数来启用和识别设计中FSM的覆盖率度量标准并进行收集。

程序

1、评估表1中的命令和开关,以确定流程所需的命令和开关

2、使用vcom或vlog编译您的设计单元。

除了设计和环境所需的任何其他命令参数之外,还包括表1中的所有开关。

3、使用vopt优化设计。

除了设计和环境所需的任何其他命令参数之外,还包括表1中的所有开关。

4、使用带有vsim命令的-coverage开关加载模拟。覆盖开关是必需的。

5、使用run命令运行仿真。

结果

vcom和vlog和vopt命令生成与任何已识别的FSM相关的消息。有关更多信息,请参阅“公认的FSM注释”和“ FSM识别信息注释”部分。

vsim命令将加载模拟并将GUI布局更改为Coverage模式。

几个GUI窗口将包含覆盖率指标。请参阅“ GUI中可用的FSM覆盖率指标”一节。

例子

在整个设计上启用FSM覆盖范围。

vcom a.vhdl b.vhdl

vcom top.vhdl

vopt + cover = f top -o opt_top

vsim -coverage opt_top

全部运行

在整个设计中启用所有类型的覆盖率。

vlog * .v

vopt +覆盖顶部-o opt_top

vsim -coverage opt_top

全部运行

在具有详细报告的完整设计上启用FSM覆盖,包括多态转换。

vcom top.vhdl

vcom a.vhdl b.vhdl

vopt + cover = f -fsmverbose -fsmmultitrans top -o opt_top

vsim -coverage opt_top

全部运行

仅在选定的设计单元上启用FSM覆盖范围。

vlog + cover = f a.v b.v

vlog top.v

vopt顶部-o opt_top

vsim -coverage opt_top

全部运行

2021.1中的基本产品规格

[支持的平台]

Linux RHEL 7 x86 / x86-64

Linux RHEL 8 x86 / x86-64

Linux SLES 12 x86 / x86-64

Windows 10 x86 / x64

[受支持的GCC编译器(用于SystemC)]

gcc-7.4.0-linux / gcc-7.4.0-linux_x86_64

gcc-5.3.0-linux / gcc-5.3.0-linux_x86_64

gcc-4.7.4-linux / gcc-4.7.4-linux_x86_64

gcc-7.4.0-mingw32vc15

gcc-7.4.0-mingw64vc15

[OVL(产品附带)]

v2.8.1

[VHDL OSVVM(产品附带)]

v2014.07

[VHDL UVVM(产品附带)]

UVVM v2019.11.25

[授权]

FLEXnet v11.16.4.0

MSL v2020_1

MGLS v9.23_5.5.0

PCLS v9.23.5.3.0

2021.1版的兼容性问题

SystemVerilog兼容性

QSIM-62783-(源)由Vlog和vopt处理的情况下,类在某些情况下与包的名称不正确。给出以下示例:

包P;

typedef逻辑type1_t;

P级

typedef逻辑type2_t;

结束类

最终包装

输入P :: *; //在$ unit范围内导入使名为“ P”的类可能可见

模块顶部;

P :: type1_t i; //这应该是一个错误,因为“ P”应该引用该类

P :: type2_t j; //这应解析为类“ P”中的类型

终端模块

正确的行为是报告P :: type1_t的错误并接受P :: type2_t,但是先前的发行版扭转了该行为。

QSIM-62590-(源)在某些情况下,带有内嵌约束的randomize()调用,如果未声明约束符号,则将插入虚拟符号,这现在标记为错误。

QSIM-65870-(源)在极少数情况下涉及参数化类,使用无效参数(不是随机类的字段)调用class :: randomize()不会在编译期间引起错误。在模拟过程中,带有非法参数的调用也将被错误地继续进行而没有任何错误。仿真时间行为已更改为检查和强制class :: randomize()的参数合法性。任何不是随机类字段的参数都将触发(vsim-7210)错误。请注意,如果需要旧的(断开的)行为,则可以抑制此新错误。

QSIM-62161-(结果)在一些极少数情况下,randomize()会错误地评估RHS上包含带索引多维数组(索引是随机的)的dist / inside / unique构造的约束。这个问题已被解决。

QSIM-62298-(结果)在少数情况下,当评估涉及dist / inside / unique的约束(其中RHS是非随机解压缩数组)时,randomize()会产生无效的解决方案。这个问题已被解决。

QSIM-62229-(结果)在某些情况下,如果使用非LRM兼容语法指定数组,则randomize()会错误地评估多维数组的迭代(foreach)约束,其中一个或多个数组维是动态的。 “ foreach(a [0] [i])”)。这个问题已被解决。

QSIM-65052-(结果)在少数情况下,当评估涉及array.sum()约束的随机化方案时,randomize()会避免从解决方案空间中选择特定的有效解决方案。这个问题已被解决。

QSIM-66481-(结果)在一些极少数情况下,当在迭代约束中指定时,randomize()会错误地评估涉及队列末端表达式($)的约束。这个问题已被解决。

QSIM-60165-(结果)当输出有关涉及打包结构的变量/约束的信息时,-solvefaildebug约束矛盾报告的输出得到了改进。过去,约束矛盾报告将打包结构的各个字段显示为部分选择。现在,报告将这些字段显示为字段名称(如果可能),从而提高了报告的可读性。

QSIM-63510-(结果)改进了求解器重播的行为(vsim -solvereplay),使得用尽重播文件后的模拟行为将与不重播的相同模拟(具有相同种子)的行为相匹配。

QSIM-66609-(结果)实施了新的vsim SystemVerilog约束随机语言扩展“ impvecindex”(指定启用“ vsim -svrandext = + impvecindex”),这将指示Questa对2状态压缩向量的随机索引注入约束/ arrays,以使索引的值在指定向量/数组的范围内。

在约束向量/数组上(在约束范围内)随机索引表达式的更新行为如下:

如果压缩数组是4状态类型(即逻辑),则对随机索引的隐式约束将被注入-这意味着随机索引的值必须是入站的(如果对随机索引有约束,则将要求它越界,就会发生约束矛盾)。在这种情况下,randomize()不可能为随机索引生成越界值。

如果压缩数组是2状态类型(即位),则不会插入对随机索引的隐式约束,并且可能将随机索引的值评估为界外-在这种情况下在这种情况下,出界位的值等于零。如果索引被评估为超出范围的值,则会显示警告。指定vsim -svrandext = + impvecindex将指示Questa注入约束,这些约束将要求随机索引为入站。

VHDL兼容性

[nodvtid]-(源)修复了一个错误,其中对别名的修改不会影响原始对象。

QSIM-67598-(源)向vcom和vopt添加了错误号1624,以在组件实例没有通用列表的组件实例上存在通用映射时向用户发出警告。以前的版本默默地忽略了通用映射。现在默认情况下会生成警告。这确实应该是一个错误,但是为了与以前的版本兼容,这只是一个警告,仍然会忽略通用映射。

[nodvtid]-(源,结果)重构了-g / -G值的处理方式,现在进行适当的大小检查以防止在值与目标对象不匹配的情况下发生意外错误。现在,如果该值不符合目标对象的约束,将发出警告。

QSIM-61007-(结果)将具有子元素关联的端口映射中的端口连接到OPEN是非法的,即使所有子元素都是OPEN。此增强功能允许不受约束的端口与子元素相关联,只要所有与OPEN相关联的子元素都可以。

这是为了使不受约束的端口受到约束。像这样的陈述

PORT MAP(OUT(1)=> OPEN)-约束到(1到1)

PORT MAP(OUT(1 to 2)=> OPEN)-约束到(1到2)

请注意,无限制端口的方向是索引范围子类型的方向,通常为TO NOT DOWNTO。

混合语言兼容性

QSIM-67008-(结果)VHDL外部名称现在可以在System Verilog范围中查找不区分大小写的名称。以前,它使用VHDL代码中标识符的大小写形式,这是不正确的。因此,如果名称仅大小写不同,则外部名称可能会以不同的方式解析。

一般相容性

QSIM-65779-(源)为uvm_hdl_check_path在-qfd模式下返回FALSE的情况添加了可抑制的错误消息。此更改可能导致一些现有的客户测试用例给出这些错误消息。使用vsim选项-suppress 16126可以禁止显示消息。

QSIM-68141-(结果)某些VCD文件包含扩展的(VHDL)标识符。vcd2wlf和vcd2qwave工具并不总是正确读取这些标识符。此问题已得到纠正。

验证管理兼容性

[nodvtid]-(结果)修改后的VRM以截断覆盖数(而不是四舍五入),以匹配其他覆盖率报告工具。

2021.1中修复的一般缺陷

QSIM-55060-在将工作库移入文件系统后,运行vopt重新生成现有的优化设计有时会产生一条错误消息,其中涉及原始文件路径名。行为已修复,vopt现在将重新生成优化的设计。

QSIM-68141-(结果)某些VCD文件包含扩展的(VHDL)标识符。vcd2wlf和vcd2qwave工具并不总是正确读取这些标识符。此问题已得到纠正。

2021.1中修复的SystemVerilog缺陷

QSIM-62161-(结果)在一些极少数情况下,randomize()会错误地评估RHS上包含带索引多维数组(索引是随机的)的dist / inside / unique构造的约束。这个问题已被解决。

QSIM-62470-在极少数情况下,带有引用静态类字段的嵌入式约束的randomize()调用会导致vopt崩溃。这个问题已被解决。

QSIM-62421-在极少数情况下,在具有“ rand”类字段且在NULL和非NULL之间切换的类上多次重复调用randomize()会导致vsim崩溃。这个问题已被解决。

QSIM-62298-(结果)在少数情况下,当评估涉及dist / inside / unique的约束(其中RHS是非随机解压缩数组)时,randomize()会产生无效的解决方案。这个问题已被解决。

QSIM-62271-在少数情况下,当评估涉及dist / inside / unique的约束(其中RHS是非随机解压缩数组)时,randomize()会导致vsim崩溃。这个问题已被解决。

QSIM-62382-在某些罕见的情况下,当评估涉及索引数组的约束时,randomize()会触发虚假错误(vsim-7066:索引超出范围)。这个问题已被解决。

QSIM-62229-(结果)在某些情况下,如果使用非LRM兼容语法指定数组,则randomize()会错误地评估多维数组的迭代(foreach)约束,其中一个或多个数组维是动态的。 “ foreach(a [0] [i])”)。这个问题已被解决。

QSIM-62312-在少数情况下,当评估包含带有随机索引的关联数组的约束时,randomize()会导致vsim崩溃。这个问题已被解决。

[nodvtid]-Vsim有时在声明体外类函数时会出现此错误,其中返回类型使用“ classname ::”引用了另一个参数化类

错误:foo.sv(12):Questa遇到意外的内部错误:../../ src / vlog /

QSIM-62117-在极少数情况下,当randomize()使用非随机LHS评估“ dist”约束时,会发生内部错误。这个问题已被解决。

QSIM-62480-对于涉及if / else约束的一些randomize()调用,其隐含(条件为true)和Alternate(条件为false)约束等效(但不相同),从而显着提高了性能。

QSIM-62633-在极少数情况下,randomize()会为涉及“!inside”约束的情况选择无效的解决方案,其中在“ inside”运算符的RHS上指定了非随机解压缩数组。这个问题已被解决。

QSIM-62967-在某些情况下,如果数组是用降序索引声明的,则randomize()会错误地评估涉及未打包元素的随机未打包数组的情况。这个问题已被解决。

QSIM-63224-在少数情况下,启用-solvefaildebug = 2时,randomize()会发出内部错误或崩溃。这个问题已被解决。

QSIM-63296-在极少数情况下,当评估涉及算术右移运算符的约束表达式时,randomize()会选择无效的解决方案。这个问题已被解决。

QSIM-63333-在极少数情况下,randomize()会触发SIGFPE或SIVSEGV崩溃。这个问题已被解决。

QSIM-63742-在极少数情况下,当评估包含涉及非随机动态数组的array.sum()表达式的约束时,randomize()会导致vsim崩溃。这个问题已被解决。

QSIM-63225-在少数情况下,当评估涉及函数调用的约束时,randomize()会导致vsim崩溃。这个问题已被解决。

QSIM-63080-在极少数情况下,使用BDD求解器引擎评估randset时,randomize()调用会导致vsim崩溃。这个问题已被解决。

QSIM-63716-显着提高了某些涉及array.sum()约束的复杂randomize()调用的性能。现在可以成功解决以前可能超时的某些randomize()方案。

QSIM-63802-在少数情况下,当评估涉及随机类的非随机类字段的约束时,randomize()会导致vsim崩溃。这个问题已被解决。

QSIM-63738-在极少数情况下,当评估涉及乘法和强制转换表达式的复杂约束时,randomize()会导致vsim崩溃。这个问题已被解决。

QSIM-63610-在极少数情况下,由于约束矛盾而导致的randomize()失败会生成一个测试用例(启用-solvefailtestcase时),该测试用例不会重现该矛盾。这个问题已被解决。

QSIM-64086-在极少数情况下,当不存在实际矛盾时,randomize()会错误地报告无解失败(约束矛盾)。这个问题已被解决。

QSIM-62783-(源)由Vlog和vopt处理的情况下,类在某些情况下与包的名称不正确。给出以下示例:

包P;

typedef逻辑type1_t;

P级

typedef逻辑type2_t;

结束类

最终包装

输入P :: *; //在$ unit范围内导入使名为“ P”的类可能可见

模块顶部;

P :: type1_t i; //这应该是一个错误,因为“ P”应该引用该类

P :: type2_t j; //这应解析为类“ P”中的类型

终端模块

正确的行为是报告P :: type1_t的错误并接受P :: type2_t,但是先前的发行版扭转了该行为。

QSIM-62590-(源)在某些情况下,带有内嵌约束的randomize()调用,如果未声明约束符号,则将插入虚拟符号,这现在标记为错误。

QSIM-64826-在极少数情况下,randomize()会生成违反涉及虚拟接口元素的约束的解决方案。这个问题已被解决。

QSIM-64538-在极少数情况下,使用BDD求解引擎评估randset时,randomize()会崩溃。这个问题已被解决。

QSIM-64417-在极少数情况下,randomize()会生成违反涉及局部自动变量的内联约束的解决方案。这个问题已被解决。

QSIM-64644-在极少数情况下,当评估涉及打包结构类型的随机变量的场景时,randomize()会遇到内部错误。这个问题已被解决。

QSIM-64586-在极少数情况下,randomize()会将if / else或“软”上下文中的“唯一”约束错误地解释为无条件的“硬”约束。这个问题已被解决。

QSIM-64319-在极少数情况下,randomize()会生成违反形式为“!({const_array内部的rand_var”)约束的解决方案。这个问题已被解决。

QSIM-64316-在极少数情况下,评估包含非随机解压缩数组的约束时,randomize()调用会崩溃。这个问题已被解决。

QSIM-64243-在少数情况下,当使用目标(LHS)类型域之外的RHS值评估'dist'约束时,randomize()会触发内部错误。这个问题已被解决。

QSIM-64160-在极少数情况下,在编译过程中,包含randomize()调用的程序包将触发错误的(vlog-2944)“在随机约束下非法的randomize()函数调用”错误。这个问题已被解决。

QSIM-64132-Vlog有时会给出错误的错误,例如:

**错误:解析文件test.sv(50)时:在范围'tpkg'中找不到名称'get_type'

对于'pkg :: typename :: get_type( ),其中“ typename”是解析为类的typedef名称。

QSIM-64922-Vlog报告了错误:

**错误:test.sv(7)在Implements子句中非法引用了接口类型C :: Intf。

如果“ C”是参数化的类类型,而“ Intf”是引用接口类的typedef名称。

QSIM-66018-在少数情况下,在评估约束中的函数调用时,randomize()会报告虚假(vsim-7090)错误(约束中状态表达式值中的X或Z无效)。这个问题已被解决。

QSIM-65455-在少数情况下,对于涉及否定的“内部”约束的随机化方案,其中一个恒定的未压缩数组作为操作数出现在RHS上(当解决方案集包含有效值时),randomize()会错误地返回0(无解)解决方案)。这个问题已被解决。

QSIM-65052-(结果)在少数情况下,当评估涉及array.sum()约束的随机化方案时,randomize()会避免从解决方案空间中选择特定的有效解决方案。这个问题已被解决。

QSIM-64985-修复了vopt中的内部错误,该错误在某些情况下会发生,其中包含包含网(线)的约束表达式。

QSIM-65623-修复了一个问题,该问题会导致randomize()错误地评估包含/包含解压缩并集的随机变量的约束。

QSIM-66481-(结果)在一些极少数情况下,当在迭代约束中指定时,randomize()会错误地评估涉及队列末端表达式($)的约束。这个问题已被解决。

QSIM-66347-在极少数情况下,randomize()会错误地评估涉及对“ associative_array.num()”的函数调用的约束。这个问题已被解决。

QSIM-65870-(源)在极少数情况下涉及参数化类,使用无效参数(不是随机类的字段)调用class :: randomize()不会在编译期间引起错误。在模拟过程中,带有非法参数的调用也将被错误地继续进行而没有任何错误。仿真时间行为已更改为检查和强制class :: randomize()的参数合法性。任何不是随机类字段的参数都将触发(vsim-7210)错误。请注意,如果需要旧的(断开的)行为,则可以抑制此新错误。

QSIM-65753-显着改善了包含约束的randomize()调用的性能(模拟cpu时间),该约束包含基数为2的幂的幂运算表达式。

QSIM-66870-Vopt会产生类似以下的错误:

**错误:test.sv(51):Questa遇到意外的内部错误:../../ src / vlog / vgencode.c(99)。

当派生类引用了嵌套在超类中的类的名称时。

QSIM-66663-如果数组模式键在分配模式中不是常量表达式,则用户将开始出错。

QSIM-67239-在极少数情况下,在多次重复调用后,randomize()调用会引发内部错误。这个问题已被解决。

QSIM-67108-在极少数情况下,涉及BDD求解器引擎的randomize()调用会导致仿真因SIGABRT而崩溃。这个问题已被解决。

QSIM-67010-在极少数情况下,randomize()会错误地评估LHS和RHS的符号度不匹配的相等约束。这个问题已被解决。

QSIM-67739-modelsim.ini中的“ SolveArrayResizeMax” [vsim]变量的值上限为10000000(1000万)。以前,此变量没有限制,将其设置为0等效于指定无限值。现在,如果将此变量设置为0或大于1000万的值,则该值将重置为最大值(1000万)。当使用randomize()以不受限制的方式调整随机动态数组/队列的大小时,进行此更改是为了防止挂起和内存不足崩溃。

QSIM-67503-在某些罕见的情况下,当评估“字符串”类型的随机变量时,randomize()会触发内部错误。这个问题已被解决。

QSIM-67392-在某些罕见的情况下,如果先前的post_randomize()调用导致随机类对象的取消分配,则randomize()在调用post_randomize()时会导致模拟崩溃。这个问题已被解决。

QSIM-67450-现在在事件控制表达式中使用对象的虚拟方法或内置方法时,将报告错误。现在,当wait语句的返回类型非唯一时,也会报告一个错误。这些更改反映了LRM 9.4.2。

QSIM-67530-针对在randomize()调用期间发出的错误消息,更改了vsim -solvefailseverity开关的行为。以前,-solvefailseverity开关仅会由于约束矛盾而影响randomize()失败的严重性-在randomize()期间遇到的所有其他错误将不受影响。更改了此开关的行为,以提高在randomize()调用期间发出的所有错误消息的严重性,这可能导致randomize()返回0结果(如果指定的严重性级别为3或4)。

QSIM-68137-在极少数情况下,randomize()调用将触发虚假(vsim-7209)错误(randomize()成功,但由于内部错误而导致中间求解失败)。这个问题已被解决。

QSIM-68074-在极少数情况下,当评估涉及随机动态数组/队列的场景时,对randomize()的调用将导致模拟崩溃。这个问题已被解决。

QSIM-68067-在极少数情况下,当评估涉及打包结构约束的方案时,randomize()会生成无效的解决方案。这个问题已被解决。

QSIM-59853-修复了当当randomize()由于约束矛盾而失败时生成的约束矛盾报告的问题-报告的约束有时会包含不直接导致矛盾的约束。这个问题已被解决。

QSIM-67432-现在支持对integer_atom_type变量(字节,shortint,int,整数,时间等)的迭代约束。

斯沃数控加工仿真软件机械电子 / 429.4M

斯沃数控加工仿真软件机械电子 / 429.4M

NAPCB(彩色抄板软件)机械电子 / 6.6M

NAPCB(彩色抄板软件)机械电子 / 6.6M

立创eda软件机械电子 / 93.2M

立创eda软件机械电子 / 93.2M

斯沃数控加工仿真软件机械电子 / 429.4M

斯沃数控加工仿真软件机械电子 / 429.4M

Altair FluxMotor 2021机械电子 / 286M

Altair FluxMotor 2021机械电子 / 286M

NAPCB(彩色抄板软件)机械电子 / 6.6M

NAPCB(彩色抄板软件)机械电子 / 6.6M

立创eda软件机械电子 / 93.2M

立创eda软件机械电子 / 93.2M

Altair FluxMotor 2021机械电子 / 286M

Altair FluxMotor 2021机械电子 / 286M

altair inspire 2021破解版(结构分析) 附安装教程机械电子 / 2662 MB

altair inspire 2021破解版(结构分析) 附安装教程机械电子 / 2662 MB

Altium Concord Pro 2021(电子元件管理工具) v4.0.1.34 破解版机械电子 / 2150 MB

Altium Concord Pro 2021(电子元件管理工具) v4.0.1.34 破解版机械电子 / 2150 MB

立创eda软件v6.4.20.6 官方版机械电子 / 45.9M

立创eda软件v6.4.20.6 官方版机械电子 / 45.9M

斯沃数控加工仿真软件机械电子 / 429.4M

斯沃数控加工仿真软件机械电子 / 429.4M

win10eplan破解加密狗下载机械电子 / 1.10G

win10eplan破解加密狗下载机械电子 / 1.10G

Antenna Magus破解版2020机械电子 / 1.83G

Antenna Magus破解版2020机械电子 / 1.83G

红外遥控编码分析仪机械电子 / 544KB

红外遥控编码分析仪机械电子 / 544KB

大宝剑串口助手机械电子 / 250KB

大宝剑串口助手机械电子 / 250KB

纸艺大师编辑器(Pepakura Designer)v4.2.4 中文版机械电子 / 17.0M

纸艺大师编辑器(Pepakura Designer)v4.2.4 中文版机械电子 / 17.0M

飞思卡尔烧写工具v13.03 绿色版机械电子 / 1.0M

飞思卡尔烧写工具v13.03 绿色版机械电子 / 1.0M

FlashDLPrint(光固化技术切片软件)v2.1.4 官方版机械电子 / 20.3M

FlashDLPrint(光固化技术切片软件)v2.1.4 官方版机械电子 / 20.3M

solidworks2019中文版(附教程)机械电子 / 10G

solidworks2019中文版(附教程)机械电子 / 10G